纳米到底有多细微?

在开始之前,要先了解纳米究竟是什么意思。在数学上,纳米是 0.000000001 米,但这是个相当差的例子,毕竟我们只看得到小数点后有很多个零,却没有实际的感觉。如果以指甲厚度做比较的话,或许会比较明显。

用标尺实际测量的话可以得知指甲的厚度约为 0.0001 米(0.1 毫米),也就是说试着把一片指甲的侧面切成 10 万条线,每条线就约等同于 1 纳米,由此可略为想象得到 1 纳米是何等的微小了。

知道纳米有多小之后,还要理解缩小工艺的用意,缩小晶体管的最主要目的,就是可以在更小的芯片中塞入更多的晶体管,让芯片不会因技术提升而变得更大;其次,可以增加处理器的运算效率;再者,减少体积也可以降低耗电量;最后,芯片体积缩小后,更容易塞入行动装置中,满足未来轻薄化的需求。

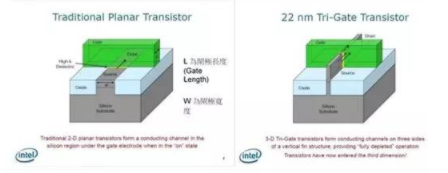

再回来探究纳米工艺是什么,以 14 纳米为例,其工艺是指在芯片中,线最小可以做到 14 纳米的尺寸,下图为传统晶体管的长相,以此作为例子。缩小晶体管的最主要目的就是为了要减少耗电量,然而要缩小哪个部分才能达到这个目的?左下图中的 L 就是我们期望缩小的部分。藉由缩小闸极长度,电流可以用更短的路径从 Drain 端到 Source 端(有兴趣的话可以利用 Google 以 MOSFET 搜寻,会有更详细的解释)。

此外,计算机是以 0 和 1 作运算,要如何以晶体管满足这个目的呢?做法就是判断晶体管是否有电流流通。当在 Gate 端(绿色的方块)做电压供给,电流就会从 Drain 端到 Source 端,如果没有供给电压,电流就不会流动,这样就可以表示 1 和 0。(至于为什么要用 0 和 1 作判断,有兴趣的话可以去查布尔代数,我们是使用这个方法作成计算机的)

尺寸缩小有其物理限制

不过,工艺并不能无限制的缩小,当我们将晶体管缩小到 20 纳米左右时,就会遇到量子物理中的问题,让晶体管有漏电的现象,抵销缩小 L 时获得的效益。作为改善方式,就是导入 FinFET(Tri-Gate)这个概念,如右上图。在 Intel 以前所做的解释中,可以知道藉由导入这个技术,能减少因物理现象所导致的漏电现象。

更重要的是,藉由这个方法可以增加 Gate 端和下层的接触面积。在传统的做法中(左上图),接触面只有一个平面,但是采用 FinFET(Tri-Gate)这个技术后,接触面将变成立体,可以轻易的增加接触面积,这样就可以在保持一样的接触面积下让 Source-Drain 端变得更小,对缩小尺寸有相当大的帮助。

最后,则是为什么会有人说各大厂进入 10 纳米制程将面临相当严峻的挑战,主因是 1 颗原子的大小大约为 0.1 纳米,在 10 纳米的情况下,一条线只有不到 100 颗原子,在制作上相当困难,而且只要有一个原子的缺陷,像是在制作过程中有原子掉出或是有杂质,就会产生不知名的现象,影响产品的良率。

如果无法想象这个难度,可以做个小实验。在桌上用 100 个小珠子排成一个 10×10 的正方形,并且剪裁一张纸盖在珠子上,接着用小刷子把旁边的的珠子刷掉,最后使他形成一个 10×5 的长方形。这样就可以知道各大厂所面临到的困境,以及达成这个目标究竟是多么艰巨。

随着三星以及台积电在近期将完成 14 纳米、16 纳米 FinFET 的量产,两者都想争夺 Apple 下一代的 iPhone 芯片代工,我们将看到相当精彩的商业竞争,同时也将获得更加省电、轻薄的手机,要感谢摩尔定律所带来的好处呢。

【半导体科普】半导体产业的根基:硅晶圆是什么?

在半导体的官方网站中,总是会提到以尺寸标示的晶圆厂,如 8 吋或是 12 吋晶圆厂,然而,所谓的晶圆到底是什么东西?其中 8 吋指的是什么部分?要产出大尺寸的晶圆制造又有什么难度呢?以下将逐步介绍半导体最重要的基础——「晶圆」到底是什么。

何谓晶圆?

晶圆(wafer),是制造各式计算机芯片的基础。我们可以将芯片制造比拟成用乐高积木盖房子,藉由一层又一层的堆栈,完成自己期望的造型(也就是各式芯片)。然而,如果没有良好的地基,盖出来的房子就会歪来歪去,不合自己所意,为了做出完美的房子,便需要一个平稳的基板。对芯片制造来说,这个基板就是接下来将描述的晶圆。

首先,先回想一下小时候在玩乐高积木时,积木的表面都会有一个一个小小圆型的凸出物,藉由这个构造,我们可将两块积木稳固的迭在一起,且不需使用胶水。芯片制造,也是以类似这样的方式,将后续添加的原子和基板固定在一起。因此,我们需要寻找表面整齐的基板,以满足后续制造所需的条件。

在固体材料中,有一种特殊的晶体结构──单晶(Monocrystalline)。它具有原子一个接着一个紧密排列在一起的特性,可以形成一个平整的原子表层。因此,采用单晶做成晶圆,便可以满足以上的需求。然而,该如何产生这样的材料呢,主要有二个步骤,分别为纯化以及拉晶,之后便能完成这样的材料。

如何制造单晶的晶圆

纯化分成两个阶段,第一步是冶金级纯化,此一过程主要是加入碳,以氧化还原的方式,将氧化硅转换成 98% 以上纯度的硅。大部份的金属提炼,像是铁或铜等金属,皆是采用这样的方式获得足够纯度的金属。但是,98% 对于芯片制造来说依旧不够,仍需要进一步提升。因此,将再进一步采用西门子制程(Siemens process)作纯化,如此,将获得半导体制程所需的高纯度多晶硅。

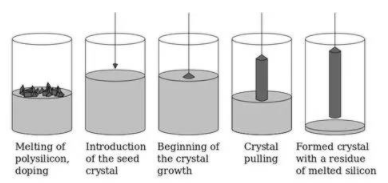

▲硅柱制造流程(Source: Wikipedia)

接着,就是拉晶的步骤。首先,将前面所获得的高纯度多晶硅融化,形成液态的硅。之后,以单晶的硅种(seed)和液体表面接触,一边旋转一边缓慢的向上拉起。至于为何需要单晶的硅种,是因为硅原子排列就和人排队一样,会需要排头让后来的人该如何正确的排列,硅种便是重要的排头,让后来的原子知道该如何排队。最后,待离开液面的硅原子凝固后,排列整齐的单晶硅柱便完成了。

单晶硅柱(Souse:Wikipedia)

然而,8吋、12吋又代表什么东西呢?他指的是我们产生的晶柱,长得像铅笔笔杆的部分,表面经过处理并切成薄圆片后的直径。至于制造大尺寸晶圆又有什么难度呢?如前面所说,晶柱的制作过程就像是在做棉花糖一样,一边旋转一边成型。有制作过棉花糖的话,应该都知道要做出大而且扎实的棉花糖是相当困难的,而拉晶的过程也是一样,旋转拉起的速度以及温度的控制都会影响到晶柱的质量。也因此,尺寸愈大时,拉晶对速度与温度的要求就更高,因此要做出高质量 12 吋晶圆的难度就比 8 吋晶圆还来得高。

只是,一整条的硅柱并无法做成芯片制造的基板,为了产生一片一片的硅晶圆,接着需要以钻石刀将硅晶柱横向切成圆片,圆片再经由抛光便可形成芯片制造所需的硅晶圆。经过这么多步骤,芯片基板的制造便大功告成,下一步便是堆栈房子的步骤,也就是芯片制造。至于该如何制作芯片呢?接着往下看。

【半导体科普】IC 芯片的制造,层层打造的高科技工艺

在介绍过硅晶圆是什么东西后,同时,也知道制造 IC 芯片就像是用乐高积木盖房子一样,藉由一层又一层的堆栈,创造自己所期望的造型。然而,盖房子有相当多的步骤,IC 制造也是一样,制造 IC 究竟有哪些步骤?本文将将就 IC 芯片制造的流程做介绍。

层层堆栈的芯片架构

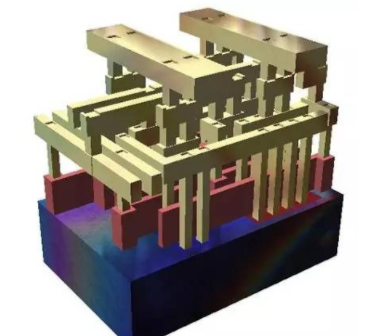

在开始前,我们要先认识 IC 芯片是什么。IC,全名集成电路(Integrated Circuit),由它的命名可知它是将设计好的电路,以堆栈的方式组合起来。藉由这个方法,我们可以减少连接电路时所需耗费的面积。下图为 IC 电路的 3D 图,从图中可以看出它的结构就像房子的梁和柱,一层一层堆栈,这也就是为何会将 IC 制造比拟成盖房子。

▲ IC 芯片的 3D 剖面图。

从上图中 IC 芯片的 3D 剖面图来看,底部深蓝色的部分就是上一篇介绍的晶圆,从这张图可以更明确的知道,晶圆基板在芯片中扮演的角色是何等重要。至于红色以及土黄色的部分,则是于 IC 制作时要完成的地方。

首先,在这里可以将红色的部分比拟成高楼中的一楼大厅。一楼大厅,是一栋房子的门户,出入都由这里,在掌握交通下通常会有较多的机能性。因此,和其他楼层相比,在兴建时会比较复杂,需要较多的步骤。在 IC 电路中,这个大厅就是逻辑闸层,它是整颗 IC 中最重要的部分,藉由将多种逻辑闸组合在一起,完成功能齐全的 IC 芯片。

黄色的部分,则像是一般的楼层。和一楼相比,不会有太复杂的构造,而且每层楼在兴建时也不会有太多变化。这一层的目的,是将红色部分的逻辑闸相连在一起。之所以需要这么多层,是因为有太多线路要连结在一起,在单层无法容纳所有的线路下,就要多迭几层来达成这个目标了。在这之中,不同层的线路会上下相连以满足接线的需求。

分层施工,逐层架构

知道 IC 的构造后,接下来要介绍该如何制作。试想一下,如果要以油漆喷罐做精细作图时,我们需先割出图形的遮盖板,盖在纸上。接着再将油漆均匀地喷在纸上,待油漆干后,再将遮板拿开。不断的重复这个步骤后,便可完成整齐且复杂的图形。制造 IC 就是以类似的方式,藉由遮盖的方式一层一层的堆栈起来。

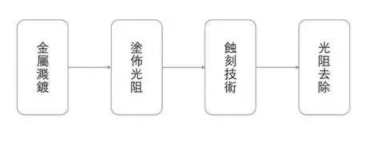

制作 IC 时,可以简单分成以上 4 种步骤。虽然实际制造时,制造的步骤会有差异,使用的材料也有所不同,但是大体上皆采用类似的原理。这个流程和油漆作画有些许不同,IC 制造是先涂料再加做遮盖,油漆作画则是先遮盖再作画。以下将介绍各流程。

1.金属溅镀:将欲使用的金属材料均匀洒在晶圆片上,形成一薄膜。

2.涂布光阻:先将光阻材料放在晶圆片上,透过光罩(光罩原理留待下次说明),将光束打在不要的部分上,破坏光阻材料结构。接着,再以化学药剂将被破坏的材料洗去。

3.蚀刻技术:将没有受光阻保护的硅晶圆,以离子束蚀刻。

4.光阻去除:使用去光阻液皆剩下的光阻溶解掉,如此便完成一次流程。

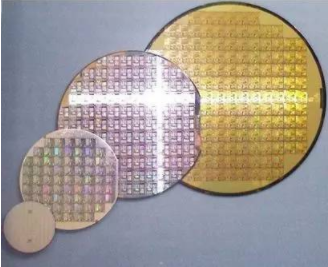

最后便会在一整片晶圆上完成很多 IC 芯片,接下来只要将完成的方形 IC 芯片剪下,便可送到封装厂做封装,至于封装厂是什么东西?就要待之后再做说明啰。

▲ 各种尺寸晶圆的比较。(Source:Wikipedia)

【半导体科普】IC 功能的关键,复杂繁琐的芯片设计流程

在前面已经介绍过芯片制造的过程就如同用乐高盖房子一样,先有晶圆作为地基,再层层往上迭的芯片制造流程后,就可产出必要的 IC 芯片。然而,没有设计图,拥有再强制造能力都没有用,因此,建筑师的角色相当重要。但是 IC 设计中的建筑师究竟是谁呢?接下来要针对 IC 设计做介绍。

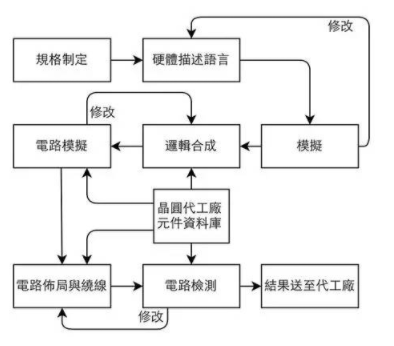

在 IC 生产流程中,IC 多由专业 IC 设计公司进行规划、设计,像是联发科、高通、Intel 等知名大厂,都自行设计各自的 IC 芯片,提供不同规格、效能的芯片给下游厂商选择。因为 IC 是由各厂自行设计,所以 IC 设计十分仰赖工程师的技术,工程师的素质影响着一间企业的价值。然而,工程师们在设计一颗 IC 芯片时,究竟有那些步骤?设计流程可以简单分成如下。

设计第一步,订定目标

在 IC 设计中,最重要的步骤就是规格制定。这个步骤就像是在设计建筑前,先决定要几间房间、浴室,有什么建筑法规需要遵守,在确定好所有的功能之后在进行设计,这样才不用再花额外的时间进行后续修改。IC 设计也需要经过类似的步骤,才能确保设计出来的芯片不会有任何差错。

规格制定的第一步便是确定 IC 的目的、效能为何,对大方向做设定。接着是察看有哪些协议要符合,像无线网卡的芯片就需要符合 IEEE 802.11 等规范,不然,这芯片将无法和市面上的产品兼容,使它无法和其他设备联机。最后则是确立这颗 IC 的实作方法,将不同功能分配成不同的单元,并确立不同单元间链接的方法,如此便完成规格的制定。

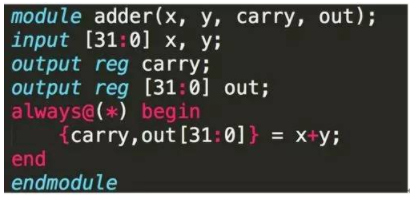

设计完规格后,接着就是设计芯片的细节了。这个步骤就像初步记下建筑的规画,将整体轮廓描绘出来,方便后续制图。在 IC 芯片中,便是使用硬件描述语言(HDL)将电路描写出来。常使用的 HDL 有 Verilog、VHDL 等,藉由程序代码便可轻易地将一颗 IC 地菜单达出来。接着就是检查程序功能的正确性并持续修改,直到它满足期望的功能为止。

▲ 32 bits 加法器的 Verilog 范例。

有了计算机,事情都变得容易

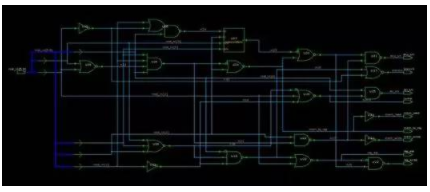

有了完整规画后,接下来便是画出平面的设计蓝图。在 IC 设计中,逻辑合成这个步骤便是将确定无误的 HDL code,放入电子设计自动化工具(EDA tool),让计算机将 HDL code 转换成逻辑电路,产生如下的电路图。之后,反复的确定此逻辑闸设计图是否符合规格并修改,直到功能正确为止。

▲ 控制单元合成后的结果。

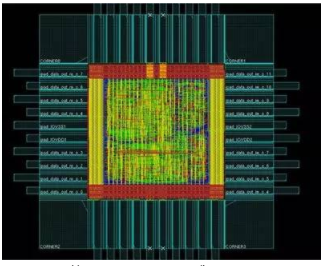

最后,将合成完的程序代码再放入另一套 EDA tool,进行电路布局与绕线(Place And Route)。在经过不断的检测后,便会形成如下的电路图。图中可以看到蓝、红、绿、黄等不同颜色,每种不同的颜色就代表着一张光罩。至于光罩究竟要如何运用呢?

▲ 常用的演算芯片- FFT 芯片,完成电路布局与绕线的结果。

层层光罩,迭起一颗芯片

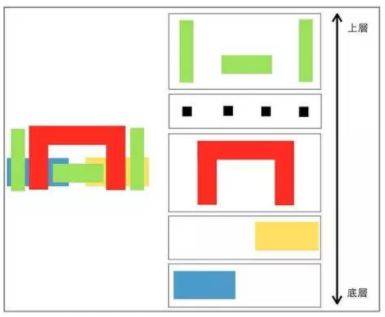

首先,目前已经知道一颗 IC 会产生多张的光罩,这些光罩有上下层的分别,每层有各自的任务。下图为简单的光罩例子,以集成电路中最基本的组件 CMOS 为范例,CMOS 全名为互补式金属氧化物半导体(Complementary metal–oxide–semiconductor),也就是将 NMOS 和 PMOS 两者做结合,形成 CMOS。至于什么是金属氧化物半导体(MOS)?这种在芯片中广泛使用的组件比较难说明,一般读者也较难弄清,在这里就不多加细究。

下图中,左边就是经过电路布局与绕线后形成的电路图,在前面已经知道每种颜色便代表一张光罩。右边则是将每张光罩摊开的样子。制作是,便由底层开始,依循上一篇 IC 芯片的制造中所提的方法,逐层制作,最后便会产生期望的芯片了。

至此,对于 IC 设计应该有初步的了解,整体看来就很清楚 IC 设计是一门非常复杂的专业,也多亏了计算机辅助软件的成熟,让 IC 设计得以加速。IC 设计厂十分依赖工程师的智能,这里所述的每个步骤都有其专门的知识,皆可独立成多门专业的课程,像是撰写硬件描述语言就不单纯的只需要熟悉程序语言,还需要了解逻辑电路是如何运作、如何将所需的算法转换成程序、合成软件是如何将程序转换成逻辑闸等问题。

在了解 IC 设计师如同建筑师,晶圆代工厂是建筑营造厂之后,接下来该暸解最终如何把芯片包装成一般用户所熟知的外观,也就是「封装」。下面将介绍 IC 封装是什么以及几个重要的技术。

【半导体科普】封装,IC 芯片的最终防护与统整

经过漫长的流程,从设计到制造,终于获得一颗 IC 芯片了。然而一颗芯片相当小且薄,如果不在外施加保护,会被轻易的刮伤损坏。此外,因为芯片的尺寸微小,如果不用一个较大尺寸的外壳,将不易以人工安置在电路板上。因此,本文接下来要针对封装加以描述介绍。

目前常见的封装有两种,一种是电动玩具内常见的,黑色长得像蜈蚣的 DIP 封装,另一为购买盒装 CPU 时常见的 BGA 封装。至于其他的封装法,还有早期 CPU 使用的 PGA(Pin Grid Array;Pin Grid Array)或是 DIP 的改良版 QFP(塑料方形扁平封装)等。因为有太多种封装法,以下将对 DIP 以及 BGA 封装做介绍。

传统封装,历久不衰

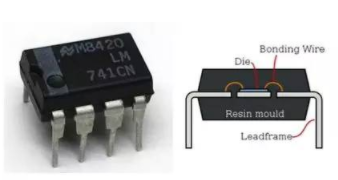

首先要介绍的是双排直立式封装(Dual Inline Package;DIP),从下图可以看到采用此封装的 IC 芯片在双排接脚下,看起来会像条黑色蜈蚣,让人印象深刻,此封装法为最早采用的 IC 封装技术,具有成本低廉的优势,适合小型且不需接太多线的芯片。但是,因为大多采用的是塑料,散热效果较差,无法满足现行高速芯片的要求。因此,使用此封装的,大多是历久不衰的芯片,如下图中的 OP741,或是对运作速度没那么要求且芯片较小、接孔较少的 IC 芯片。

▲ 左图的 IC 芯片为 OP741,是常见的电压放大器。右图为它的剖面图,这个封装是以金线将芯片接到金属接脚(Leadframe)。(Source :左图Wikipedia、右图Wikipedia)

至于球格数组(Ball Grid Array,BGA)封装,和 DIP 相比封装体积较小,可轻易的放入体积较小的装置中。此外,因为接脚位在芯片下方,和 DIP 相比,可容纳更多的金属接脚,相当适合需要较多接点的芯片。然而,采用这种封装法成本较高且连接的方法较复杂,因此大多用在高单价的产品上。

▲ 左图为采用 BGA 封装的芯片,主流的 X86 CPU 大多使用这种封装法。右图为使用覆晶封装的 BGA 示意图。(Source: 左图Wikipedia)

行动装置兴起,新技术跃上舞台

然而,使用以上这些封装法,会耗费掉相当大的体积。像现在的行动装置、穿戴装置等,需要相当多种组件,如果各个组件都独立封装,组合起来将耗费非常大的空间,因此目前有两种方法,可满足缩小体积的要求,分别为 SoC(System On Chip)以及 SiP(System In Packet)。

在智能型手机刚兴起时,在各大财经杂志上皆可发现 SoC 这个名词,然而 SoC 究竟是什么东西?简单来说,就是将原本不同功能的 IC,整合在一颗芯片中。藉由这个方法,不单可以缩小体积,还可以缩小不同 IC 间的距离,提升芯片的计算速度。至于制作方法,便是在 IC 设计时间时,将各个不同的 IC 放在一起,再透过先前介绍的设计流程,制作成一张光罩。

然而,SoC 并非只有优点,要设计一颗 SoC 需要相当多的技术配合。IC 芯片各自封装时,各有封装外部保护,且 IC 与 IC 间的距离较远,比较不会发生交互干扰的情形。但是,当将所有 IC 都包装在一起时,就是噩梦的开始。IC 设计厂要从原先的单纯设计 IC,变成了解并整合各个功能的 IC,增加工程师的工作量。此外,也会遇到很多的状况,像是通讯芯片的高频讯号可能会影响其他功能的 IC 等情形。

此外,SoC 还需要获得其他厂商的 IP(intellectual property)授权,才能将别人设计好的组件放到 SoC 中。因为制作 SoC 需要获得整颗 IC 的设计细节,才能做成完整的光罩,这同时也增加了 SoC 的设计成本。或许会有人质疑何不自己设计一颗就好了呢?因为设计各种 IC 需要大量和该 IC 相关的知识,只有像 Apple 这样多金的企业,才有预算能从各知名企业挖角顶尖工程师,以设计一颗全新的 IC,透过合作授权还是比自行研发划算多了。

折衷方案,SiP 现身

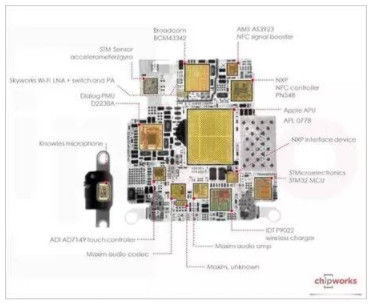

作为替代方案,SiP 跃上整合芯片的舞台。和 SoC 不同,它是购买各家的 IC,在最后一次封装这些 IC,如此便少了 IP 授权这一步,大幅减少设计成本。此外,因为它们是各自独立的 IC,彼此的干扰程度大幅下降。

▲ Apple Watch 采用 SiP 技术将整个计算机架构封装成一颗芯片,不单满足期望的效能还缩小体积,让手表有更多的空间放电池。(Source:Apple 官网)

采用 SiP 技术的产品,最著名的非 Apple Watch 莫属。因为 Watch 的内部空间太小,它无法采用传统的技术,SoC 的设计成本又太高,SiP 成了首要之选。藉由 SiP 技术,不单可缩小体积,还可拉近各个 IC 间的距离,成为可行的折衷方案。下图便是 Apple Watch 芯片的结构图,可以看到相当多的 IC 包含在其中。

▲ Apple Watch 中采用 SiP 封装的 S1 芯片内部配置图。(Source:chipworks)

完成封装后,便要进入测试的阶段,在这个阶段便要确认封装完的 IC 是否有正常的运作,正确无误之后便可出货给组装厂,做成我们所见的电子产品。至此,半导体产业便完成了整个生产的任务。